### ISA simulation CPU

- 24-bit

- Written in Python

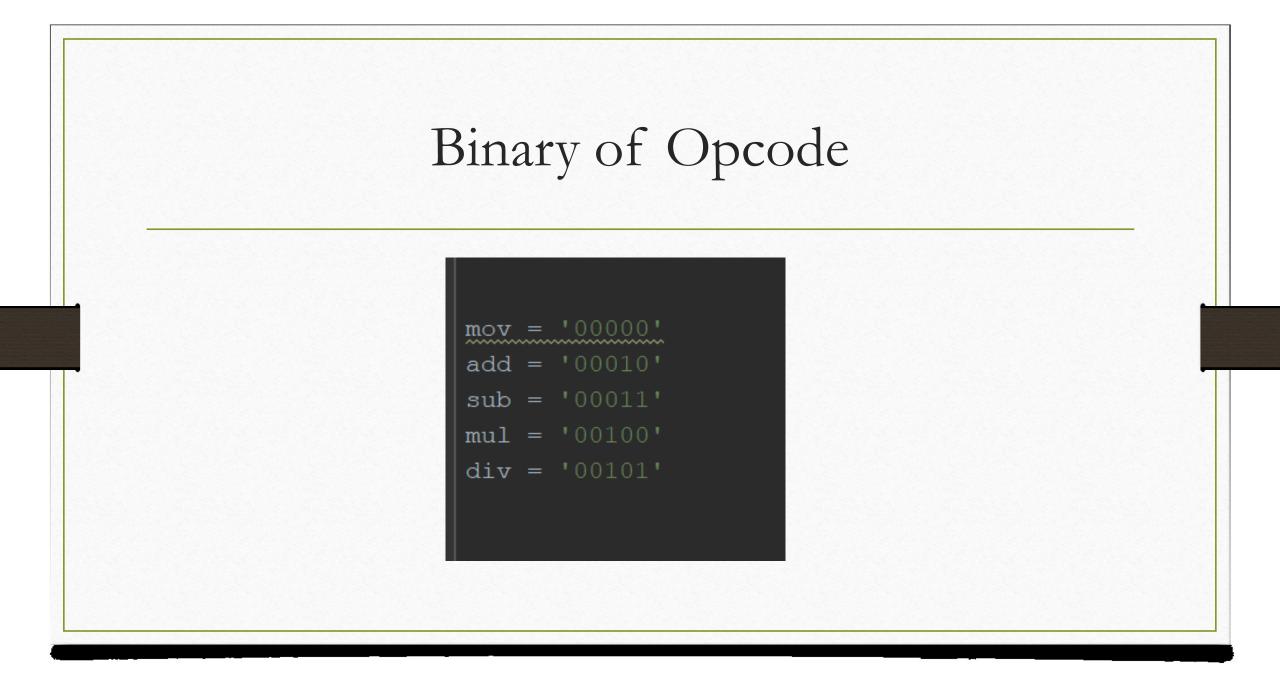

| Opcode<br>5-bits    |

|---------------------|

| Operand-1<br>3-bits |

|                     |

Registers

• 8 registers

register\_operands = []

register\_operands.append('000')

register\_operands.append('001')

register\_operands.append('010')

register\_operands.append('011')

register\_operands.append('100')

register\_operands.append('101')

register\_operands.append('111')

#### mov

- Operand 1 and Operand 2 mov r1 r3 means move register 1 into register 3

- Operand 1 and Value

mov r1 -6 means move the value -6 into register 1

### add

• Operand 1 and Operand 2

add r4 r2 means add the value of register 4 and register 2, then store the value in register 4.

• Operand 1 and Value

add r2 1 means add the value of register 4 with 1 and store the value in register 4

#### sub

• Operand 1 and Operand 2

sub r3 r2 means subtract value of register 3 with register 2 and store the value in register 3.

• Operand 1 and Value

sub r3 5 means subtract the value of register 3 with 5 and store the value in register 3.

#### mul

• Operand 1 and Operand 2

mul r6 r7 means multiply the value in register 6 and register 7 and store the 32-bit binary number of the multiplication in register 6

• Operand 1 and Value

mul r6 8 means multiply the value in register 6 with 8 and store the 32-bit binary number of the multiplication

## Div

• Operand 1 and Operand 2

div r7 r3 means divide the value of register 7 and register 3 and store the divided value in register 7

• Operand 1 and Value

div r2 4 means divide the value of register 2 with 4 and store the divided value in register 2

| Sample Input           |  |

|------------------------|--|

| mov r0 8               |  |

| mov r2 10<br>sub r2 r0 |  |

| mov r3 r0              |  |

| mul r3 2               |  |

| mov r6 r3              |  |

| div r6 2               |  |

| mov r5 r6              |  |

| end 0 0                |  |

## Sample Output

Enter the Assembly Code Opcode -> mov, add, sub, mul, div Operands -> r1 to r7 Decoded Encoded Instruction(24-bit): Clock Cycles PC[0]-> mov r0 8 00000 000 00000000000000000 1 PC[1]-> mov r2 10 00000 010 00000000000001010 1  $PC[2] \rightarrow sub r2 r0$ 00011 010 00000000000000000 2 PC[3]-> mov r3 r0 00000 011 00000000000000000 1 PC[4]-> mul r3 2 00100 011 0000000000010000 PC[5]-> mov r6 r3 1 PC[6]-> div r6 2 00101 110 0000000000001000 4 00000 101 00000000000001000 PC[7]-> mov r5 r6 1 Register Steps r0: 8[000000000001000] r2: 10[000000000001010] r2: 2[000000000000000]0] r3: r0[00000000000000] r6: 8.0[00000000000000] re:r6[0000000000000000] r5: r6[000000000001000]

### Final Register Result/CPI

- r0 [0000000000001000]

- r1 [0000000000000000]

- r2 [000000000000000]0]

- r3 [00000000000000000000000000000000000]

- r4 [0000000000000000]

- r5 [0000000000001000]

- r6 [0000000000001000]

- r7 [000000000000000]

CPI of Program: 1.875

### Sample Code

#### def dec\_to\_32bin(n): digit = '' if int(n) < 0: return two\_complement() while n != 0: temp = n % 2 digit += str(temp) n = n // 2 z = 32 - len(digit) for i in range(z): digit += '0' return digit[::-1]

```

def dec to bin(n):

digit = ''

if int(n) < 0:

return two_complement

while n != 0:

temp = n % 2

digit += str(temp)

n = n // 2

z = 16 - len(digit)

for i in range(z):

digit += '0'

return digit[::-1]

```

#### f two\_complement(n):

n = dec\_to\_bin(abs(n))

return complement(n)

#### f complement(n)

carry\_bit = 0

temp = ''

for j in range(len(n)):

if n[i] == '0':

temp += '1'

else:

temp += '0'

temp\_2 = ''

temp\_2 = ''

temp\_2 = ' ''

temp\_2 += '0'

carry\_bit = 1

elif i == 0 and temp[i] == '1':

temp\_2 += '0'

carry\_bit = 0

else:

if carry\_bit == 1 and temp[i] == '0':

temp\_2 += '1'

carry\_bit = 0

else:

if carry\_bit == 1 and temp[i] == '0':

temp\_2 += '1'

carry\_bit = 1

elif carry\_bit = 1 and temp[i] == '1'

temp\_2 += '1'

carry\_bit = 1

elif carry\_bit = 1

elif carry\_bit = 1

else:

temp\_2 += '0'

carry\_bit = 1

else:

temp\_2 += temp[i]

temp\_2 = temp\_2[::-1]

#### if n == 'r0': if n == 'r0': return True elif n == 'r1': return True elif n == 'r2': return True elif n == 'r3': return True elif n == 'r4': return True elif n == 'r5': return True elif n == 'r6': return True elif n == 'r7': return True elise: return False def register\_operand2(<u>r\_names</u>, r):

# Sample Code

| print ('Enter the Assembly Code')                        |

|----------------------------------------------------------|

| <pre>print('Opcode -&gt; mov, add, sub, mul, div')</pre> |

| <pre>print('Operands -&gt; r1 to r7')</pre>              |

| user_input = None                                        |

| opcode = []                                              |

| operand1 = []                                            |

| operand2 = []                                            |

| registers = ['000000000000000'] * 8                      |

| r_names = []                                             |

| r_names.append('r0')                                     |

| r_names.append('r1')                                     |

| r_names.append('r2')                                     |

| r_names.append('r3')                                     |

| r_names.append('r4')                                     |

| r_names.append('r5')                                     |

| r_names.append('r6')                                     |

| r_names.append('r7')                                     |

| while user_input != 'end 0 0':                           |

| user_input = input()                                     |

| <pre>op, opr1, opr2 = user_input.split(' ')</pre>        |

| opcode.append(op)                                        |

| operand1.append(opr1)                                    |

| operand2.append(opr2)                                    |

| index = []                                               |

| register_steps = []                                      |

| <pre>for i in range(len(operand1)):</pre>                |

| <pre>for j in range(len(r_names)):</pre>                 |

| <pre>if operand1[i] == r_names[j]:</pre>                 |

| index.append(j)                                          |

| r i in range(len(opcode)-1):            |                                                |                                                     |                    |          |

|-----------------------------------------|------------------------------------------------|-----------------------------------------------------|--------------------|----------|

|                                         |                                                |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

| temp = register_op                      |                                                |                                                     |                    |          |

|                                         | ]] = registers[temp]                           |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

|                                         | ex[i]] = two_complement(int(operand2[i]))      |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

|                                         |                                                | <pre>mov, register_operands[index[i]], regist</pre> | ers[index[i]],' ', | cpi_mov) |

|                                         |                                                |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

|                                         | ecker(operand2[i])                             |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

| temp_2 = registers                      |                                                |                                                     |                    |          |

| temp_2 = bin_to_de                      |                                                |                                                     |                    |          |

| temp_3 = registers                      |                                                |                                                     |                    |          |

| temp_3 = bin_to_de<br>temp 2 = temp 2 + |                                                |                                                     |                    |          |

|                                         | ]] = dec to bin(temp 2)                        |                                                     |                    |          |

| else:                                   | ]] - dec_to_bin(temp_2)                        |                                                     |                    |          |

|                                         | (registers[index[i]])                          |                                                     |                    |          |

| temp = temp + int                       |                                                |                                                     |                    |          |

|                                         | ]] = dec to bin(int(temp))                     |                                                     |                    |          |

|                                         | ('r' + str(index[i]) + ': '+ str(temp) + '[' + | <pre>str(registers[index[i]]) + ']')</pre>          |                    |          |

|                                         |                                                |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

|                                         |                                                |                                                     |                    |          |

# Sample Code

| checker = register_checker(operand2[i])                                                                                  |                                                             |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| if checker:                                                                                                              |                                                             |

| <pre>temp = register_operand2(r_names, operand2[i])</pre>                                                                |                                                             |

| <pre>temp_2 = registers[index[i]]</pre>                                                                                  |                                                             |

| <pre>temp_2 = bin_to_dec(temp_2)</pre>                                                                                   |                                                             |

| <pre>temp_3 = registers[temp]</pre>                                                                                      |                                                             |

| <pre>temp_3 = bin_to_dec(temp_3)</pre>                                                                                   |                                                             |

| <pre>temp_2 = int(temp_2 / int(temp_3))</pre>                                                                            |                                                             |

| <pre>remainder = int(temp_2) % int(temp_3)</pre>                                                                         |                                                             |

| registers[index[i]] = dec_to_bin(temp_2)                                                                                 |                                                             |

| register_steps.append('r' + str(index[i]) + ': ' + str(temp_2) + '[' + str(registers[index[i]]) + ']' +                  | re:' + 'r' + str(index[i]) + '[' + str(dec_to_bin(remainde  |

|                                                                                                                          |                                                             |

| <pre>val = registers[index[i]]</pre>                                                                                     |                                                             |

| <pre>temp = bin_to_dec(val)</pre>                                                                                        |                                                             |

| <pre>temp = int(temp) / int(operand2[i])</pre>                                                                           |                                                             |

| <pre>remainder = int(temp) % int(operand2[i])</pre>                                                                      |                                                             |

| registers[index[i]] = dec_to_bin(int(temp))                                                                              |                                                             |

| register_steps.append('r' + str(index[i]) + ': ' + str(temp) + '[' + str(registers[index[i]]) + ']' + ' re               | e:'_+ 'r' + str(index[i]) + '[' + str(dec_to_bin(remainder) |

| <pre>print('PC['+str(i)+']-&gt; ', opcode[i], operand1[i], operand2[i],' ', div, register_operands[index[i]], regi</pre> | <pre>sters[index[i]]<sub>4</sub>' ', cpi_div)</pre>         |

|                                                                                                                          |                                                             |

|                                                                                                                          |                                                             |

| <pre>for i in range(len(register_steps)):</pre>                                                                          |                                                             |

| <pre>print(register_steps[i])</pre>                                                                                      |                                                             |

|                                                                                                                          |                                                             |

|                                                                                                                          |                                                             |

|                                                                                                                          |                                                             |

| <pre>for i in range(len(registers)):</pre>                                                                               |                                                             |

| <pre>print('r' + str(i), '[' + str(registers[i]) + ']')</pre>                                                            |                                                             |

| CPI = CPI/counter                                                                                                        |                                                             |

|                                                                                                                          |                                                             |

|                                                                                                                          |                                                             |

|                                                                                                                          |                                                             |